# EFFICIENT AND VERIFIABLE TIMING CHANNEL PROTECTION FOR MULTI-CORE PROCESSORS

A Dissertation

Presented to the Faculty of the Graduate School

of Cornell University

in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy

by

Yao Wang

January 2017

© 2017 Yao Wang ALL RIGHTS RESERVED

## EFFICIENT AND VERIFIABLE TIMING CHANNEL PROTECTION FOR MULTI-CORE PROCESSORS

Yao Wang, Ph.D.

Cornell University 2017

Modern computing systems are becoming increasingly vulnerable to timing channel attacks that leak confidential information through the timing of microarchitectural events. Many timing channel attacks are caused by the interference between different programs in the shared resources of a multi-core processor. For example, an attacker program's cache lines can be evicted by a victim program, which allows the attacker to infer secret information about the victim. Timing channel attacks pose serious threats to contemporary computing systems because they can bypass traditional defense mechanisms such as access control. Previous studies have even demonstrated a practical timing channel attack to recover the keystrokes of a user in the commercial Amazon EC2 cloud.

In this thesis, we explored new timing channel attacks and developed timing channel protection schemes for some of the hardware resources in a multi-core processor. Specifically, we discovered new timing channel attacks in the shared on-chip networks and memory controllers. We proposed multiple protection mechanisms for on-chip networks, caches and memory controllers. Our protection schemes cover three high-level approaches: bi-directional protections, unidirectional protections and protections that trade off security for performance. We evaluate our protection schemes and show that the proposed schemes are effective against timing channel attacks while achieving performance improvements over previous protection schemes. Finally, we implemented some of the protection mechanisms in RTL and used SecVerilog to verify the information flow control in hardware. The results show that the protection mechanisms indeed remove timing channels at the gate level.

## **BIOGRAPHICAL SKETCH**

Yao Wang received his Bachelor of Science (with Honors) degree in Electronic Engineering from Tsinghua University in 2010. After that, he began to pursue his doctoral degree at Cornell University in the department of Electrical and Computer Engineering, with a focus on timing channel protection and hardware security. This document is dedicated to my parents and my beloved wife, Xi Yan.

#### ACKNOWLEDGEMENTS

Six years ago, I arrived at the US for the first time as a student to pursue a PhD degree in computer engineering. I can still remember that I could barely speak English at that time, and was a bit frightened by the unfamiliar environment. Six years later, I have published seven research papers and managed to finish this 200-page long thesis. To be honest, I feel quite proud of myself. But I am also clearly aware that these achievements would not have been possible without the help of many people, whom I feel fortunate to meet in my life.

I would like to express my deepest thanks and appreciation to my PhD advising committee members for the help and support they generously provided. First and foremost, I want to thank my advisor Professor Edward Suh. Ed showed me that a good researcher is rigorous, passionate, and hardworking. I do not dare to say I am a good researcher, but I was certainly getting closer and closer to the standard under Ed's guidance in the past six years. One thing I did not enjoy in graduate school was the very night before a paper deadline, but Ed was always by my side, working with me together, which certainly made some pleasant memories about the not-so-pleasant paper deadlines. I also would like to thank Ed for being so kind and tolerant with me. I made plenty of mistakes during my PhD studies, but Ed was always very gentle and patient when advising me to avoid those mistakes. The next person on my thank list is Professor Christopher Batten. In my first year, I was very fortunate to take Chris's class of Computer Architecture, which I consider as one of the best classes out there. Due to my language issue, I was falling behind and almost lost faith in myself. Chris may have noticed that and gave me some encouragements that I desperately needed at that moment. I really appreciate the help. I also want to thank Chris for the many things he did for the CSL (Computer Systems Lab) community, which was really not an easy effort. Last but not least, I would like to thank Professor Andrew Myers. It was an honor to work and interact with Andrew in the last couple of years in my PhD. I enjoyed every discussion we had on our research collaborations. I also want to thank Andrew for being very understanding and encouraging, providing help and support when I needed.

I would like to thank all CSL professors. Special thanks to Professor Dave Albonesi. His class of memory systems was a lot of fun and gave me confidence in myself. Another special thanks to Professor Jose Martinez for teaching me the interesting and painful cache coherence protocols. I also want to thank Professor Zhiru Zhang for his help and guidance. Outside of CSL, I was fortunate to interact with some of the best professors in Cornell University and I thank all of them. I specially want to thank Professor Kevin Tang for his guidance in my first couple of years in graduate school.

I felt quite honored to be part of the CSL community. During my six years of PhD studies, I witnessed senior students graduating and new faces showing up, many of whom have helped me enormously in this long journey. I want to thank everyone in Suh Research Group for contributing to my research ideas. It was a great pleasure collaborating with these guys. I want to thank Ruirui Huang and KK Yu for being such good friends and sharing their PhD experiences as senior students. I also would like to thank Daniel Lo for generously helping me with technical questions and providing insightful suggestions throughout my PhD studies. Special thanks to Andrew Ferraiuolo and Benjamin Wu, whom I have the privilege to work with. Thanks also goes to Tao, of course, for sharing ideas on new technologies and providing great suggestions all the time. I also thank Rui Xu for his pioneer work on using SecVerilog. Outside of my research group, I was grateful to meet some of the best people in my life. Saugata Ghose was always ready to provide help whenever I needed. He was such a reliable friend. The same goes to Shreesha Srinath. I enjoyed every lunch conversation we had and of course, thank you so much for letting me stay in your house before my thesis defense. I also want to thank Rob Karmarzin for being such a trustworthy officemate and introducing my cat, BaBao, to me and my wife. Special thanks to Maia Kelner, who very patiently taught me how to drive and familiarized me with American culture. There were so many people who have helped me along the way that it will be overly long if I enumerate all of them—Jon Tse, Ben Hill, Xiaodong Wang, Ji Kim, Berkin Ilbeyi, just to name a few. I wish all the students in CSL can succeed in their future endeavors.

I also had the opportunities to work with some brilliant students outside of CSL. Danfeng Zhang, who is now a professor in Pennsylvania State University, had collaboration with me on several research projects. I enjoyed our collaboration a lot and also learned about language-based security from him. I would like to also thank Nithin Micheal, whom I was grateful to work with in my early research projects.

Finally, I wish to express my deepest thanks to my family. My parents, Sixue Wang and Mingyao Qian, taught me the importance of self-discipline and hard-working, which got me this far in my academic journey. Thanks so much for raising me up and supporting me in all these years. My wife, Xi Yan, has always been by my side and backing me up. She is the one who gives me the strength and courage to overcome any difficulties I may face. I love her with all my heart.

|   | Ded<br>Ack<br>Tabl<br>List | ication<br>nowledg<br>e of Con<br>of Tables           | gements                                     | iii<br>iv<br>v<br>iii<br>xi                        |

|---|----------------------------|-------------------------------------------------------|---------------------------------------------|----------------------------------------------------|

| 1 | Intr                       | oductior                                              | 1                                           | 1                                                  |

|   | 1.1                        | A Case                                                | Study on Realistic Timing Channel Attacks   | 2                                                  |

|   |                            |                                                       | Ristenpart's Attack on Amazon's EC2         | 3                                                  |

|   |                            |                                                       | Other Realistic Timing Channel Attacks      | 8                                                  |

|   | 1.2                        |                                                       |                                             | 10                                                 |

|   |                            | 1.2.1                                                 | Baseline Architecture                       | 10                                                 |

|   |                            | 1.2.2                                                 | Hierarchical Security Policy                | 11                                                 |

|   |                            | 1.2.3                                                 | Attack Assumptions                          | 14                                                 |

|   | 1.3                        |                                                       |                                             | 15                                                 |

|   | 1.4                        | Thesis (                                              | Contribution and Organization               | 18                                                 |

|   | 1.5                        | Collabo                                               | pration, Previous Publications, and Funding | 21                                                 |

| 2 | On-<br>2.1<br>2.2<br>2.3   | 2.1.2<br>Tempor<br>Reverse<br>2.3.1<br>2.3.2<br>2.3.3 | On-chip Network Interference                | 24<br>24<br>26<br>27<br>28<br>29<br>29<br>30<br>31 |

| 3 | Cac                        |                                                       |                                             | 36                                                 |

|   | 3.1                        | Attacks                                               |                                             | 36                                                 |

|   |                            |                                                       |                                             | 36                                                 |

|   |                            |                                                       |                                             | 37                                                 |

|   | ~ ~                        |                                                       |                                             | 39                                                 |

|   | 3.2                        |                                                       |                                             | 40                                                 |

|   | 3.3                        |                                                       |                                             | 41<br>12                                           |

|   |                            |                                                       |                                             | 12<br>14                                           |

|   | 2.4                        |                                                       |                                             | 14<br>15                                           |

|   | 3.4                        |                                                       |                                             | 45<br>15                                           |

|   |                            |                                                       | 0                                           | 45<br>1                                            |

|   |                            | 3.4.2                                                 | SecDCP for Two Security Domains             | <del>1</del> 6                                     |

## TABLE OF CONTENTS

|   |     | 3.4.3          | SecDCP for General Case                                |

|---|-----|----------------|--------------------------------------------------------|

|   |     | 3.4.4          | Evaluation                                             |

|   | 3.5 | Protec         | ction Based on a High-Associativity Cache (ZCache) 62  |

|   |     | 3.5.1          | Background                                             |

|   |     | 3.5.2          | Same-Domain Replacement                                |

|   |     | 3.5.3          | Strict Same-Domain Replacement                         |

|   | 3.6 | Defen          | Iding Against Timing Channels within a Program 69      |

|   |     | 3.6.1          | Reuse-Based Attacks                                    |

|   |     | 3.6.2          | Language-Based Protection                              |

|   |     | 3.6.3          | Baseline Partitioned Cache                             |

|   |     | 3.6.4          | Problem: Dirty Bit Leakage                             |

|   |     | 3.6.5          | Solution 1: Mark All Cache Lines Dirty (DirtyCache) 74 |

|   |     | 3.6.6          | Solution 2: Use Relative Dirty Bits (RelCache) 76      |

| 4 |     |                |                                                        |

| 4 | 4.1 | -              | controllers 82<br>ks                                   |

|   | 4.1 | 4.1.1          |                                                        |

|   |     |                | 5                                                      |

|   |     | 4.1.2          | A Side-Channel Attack on RSA                           |

|   | 4.0 | 4.1.3          | A Covert-Channel Attack                                |

|   | 4.2 | _              | oral Partitioning (TP)                                 |

|   |     | 4.2.1          | Protection Mechanisms                                  |

|   |     | 4.2.2          | Performance Optimizations                              |

|   | 4.0 | 4.2.3          | Evaluation                                             |

|   | 4.3 |                | C-NI                                                   |

|   |     | 4.3.1          | Existing Protection Schemes                            |

|   |     | 4.3.2          | SecMC-NI Algorithm                                     |

|   |     | 4.3.3          | Peak Bandwidth Comparison                              |

|   | 4 4 | 4.3.4          | Evaluation                                             |

|   | 4.4 | 4.4.1          | C-Bound                                                |

|   |     |                | Intuition and Overview                                 |

|   |     | 4.4.2          | SecMC-Bound Algorithm                                  |

|   |     | 4.4.3<br>4.4.4 | Performance Optimizations                              |

|   |     |                | Information Theoretic Bound131Evaluation133            |

|   |     | 4.4.5          | Evaluation                                             |

| 5 | RTI | . Verifi       | cation 145                                             |

|   | 5.1 | Backg          | ground: SecVerilog                                     |

|   |     | 5.1.1          | SecVerilog Examples                                    |

|   |     | 5.1.2          | Implicit Declassification                              |

|   | 5.2 | A Sin          | gle-Core MIPS Processor                                |

|   |     | 5.2.1          | Processor Design                                       |

|   |     | 5.2.2          | Overhead of Timing Channel Protection                  |

|   | 5.3 | A Mu           | lti-Core PARC-tiny Processor                           |

|   |     | 5.3.1          | Baseline Architecture                                  |

|   |     |                |                                                        |

|    |                 | 5.3.2   | Protection Mechanisms                           | 158 |

|----|-----------------|---------|-------------------------------------------------|-----|

|    |                 | 5.3.3   | SecVerilog Verification                         | 161 |

| 6  | Rela            | ted Wo  | ork                                             | 164 |

|    | 6.1             | Timing  | g Channel Attacks                               | 164 |

|    |                 |         | Software Timing Channels                        |     |

|    |                 | 6.1.2   | Hardware Timing Channels                        |     |

|    | 6.2             | Timing  | g Channel Protection                            |     |

|    |                 | -       | Software Approaches                             |     |

|    |                 | 6.2.2   | Hardware Approaches                             |     |

|    | 6.3             | Verifia | ble Hardware Information Flow Control           |     |

| 7  | Con             | clusion | L                                               | 176 |

|    | 7.1             | Summ    | ary                                             | 176 |

|    | 7.2             |         | Directions                                      |     |

|    |                 | 7.2.1   | Efficient Timing Channel Protections            | 177 |

|    |                 | 7.2.2   | QoS Support with Timing Channel Protections     |     |

|    |                 | 7.2.3   | Verifiable Information Flow Control in Hardware | 179 |

| Bi | Bibliography 18 |         |                                                 | 180 |

## LIST OF TABLES

| 1.1 | Primary contributions of this thesis                        | 21  |

|-----|-------------------------------------------------------------|-----|

| 3.1 | System configuration.                                       | 55  |

| 3.2 | Program categorization.                                     | 55  |

| 3.3 | Hash values for each address.                               | 63  |

| 4.1 | Close-page DRAM timing analysis.                            | 93  |

| 4.2 | Configuration parameters for ZSim and DRAMSim2 simulators.  | 99  |

| 4.3 | Bandwidth utilization comparison between different schemes. | 115 |

| 4.4 | Mixed workloads.                                            | 134 |

| 5.1 | Lines of Code (LOC) for each processor component            | 151 |

| 5.2 | Complete ISA of our MIPS processor.                         | 152 |

| 5.3 | Comparing processor designs.                                | 154 |

| 5.4 | Complete ISA of the PARC-tiny processor.                    | 158 |

| 5.5 | Lines of Code (LOC) for each processor component            | 161 |

| 5.6 | Extra lines due to lack of bit-level label support          | 163 |

## LIST OF FIGURES

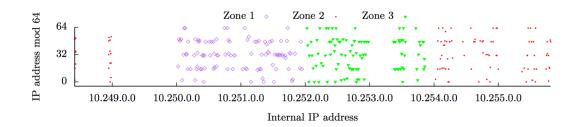

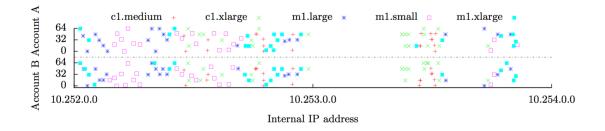

| 1.1                    | Internal IP address mapping regarding availability zones [RTSS09].                                              | 5  |

|------------------------|-----------------------------------------------------------------------------------------------------------------|----|

| 1.2                    | Internal IP address mapping regarding instance types [RTSS09].                                                  | 5  |

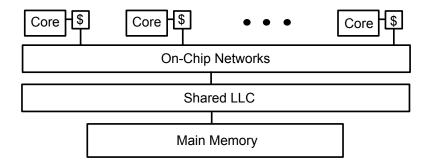

| 1.3                    | Baseline architecture.                                                                                          | 11 |

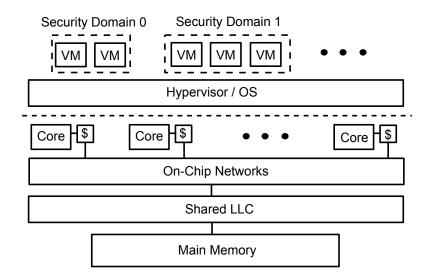

| 1.4                    | Security domains in cloud computing.                                                                            | 12 |

| 1.5                    | Hierarchical security policy.                                                                                   | 12 |

| 1.6                    | Common security policies.                                                                                       | 13 |

| 2.1                    | A simple network interference example.                                                                          | 25 |

| 2.2                    | A side-channel attack on RSA                                                                                    | 26 |

| 2.3                    | Flow A's throughput over time with varying demands from<br>Flow B. Flow A: low security, Flow B: high security. | 32 |

| 2.4                    | Experimental setup in a 6-by-6 mesh network.                                                                    | 33 |

| 2. <del>1</del><br>2.5 | Low security (domain A) throughput as a function of the high                                                    | 55 |

| 2.0                    | security (domain B) demand for transpose traffic pattern.                                                       | 34 |

| 2.6                    | Impacts of timing channel protection on the network throughput.                                                 | 35 |

| 2.0                    |                                                                                                                 | 55 |

| 3.1                    | Attack model for internal interference                                                                          | 37 |

| 3.2                    | Attack model for external interference                                                                          | 39 |

| 3.3                    | System architecture for a cache coherence attack                                                                | 42 |

| 3.4                    | SD0's timing observation                                                                                        | 43 |

| 3.5                    | Two security domains                                                                                            | 46 |

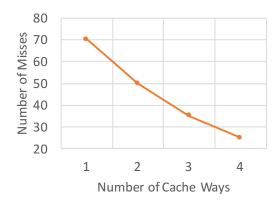

| 3.6                    | Generated miss curve by UMON                                                                                    | 47 |

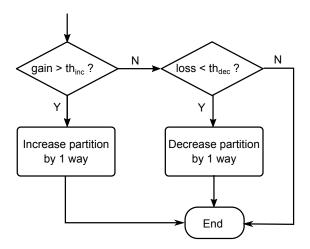

| 3.7                    | Partition Allocation Algorithm.                                                                                 | 48 |

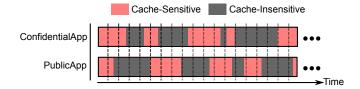

| 3.8                    | Application Phases.                                                                                             | 50 |

| 3.9                    | Security policy example                                                                                         | 52 |

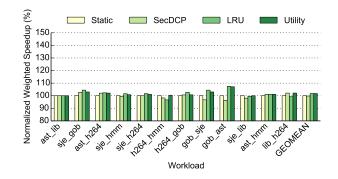

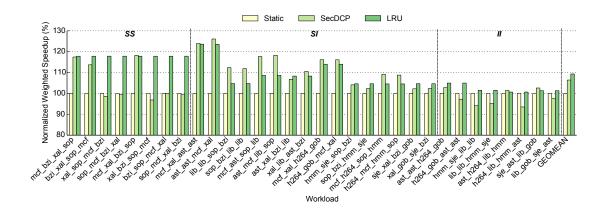

| 3.10                   | Performance for <i>SS</i> workloads.                                                                            | 56 |

| 3.11                   | Performance for <i>SI</i> workloads                                                                             | 57 |

| 3.12                   | Performance for <i>II</i> workloads                                                                             | 58 |

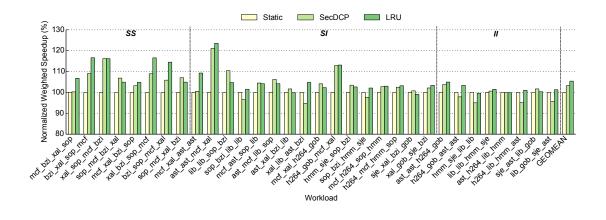

| 3.13                   | Performance for a linear security policy                                                                        | 59 |

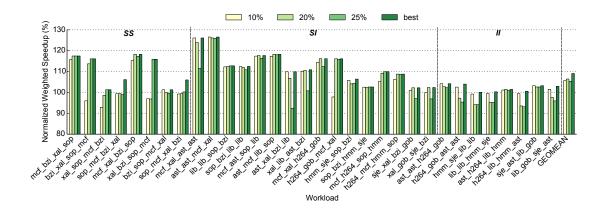

| 3.14                   | Performance with different thresholds.                                                                          | 60 |

| 3.15                   | Performance for mobile security policy.                                                                         | 61 |

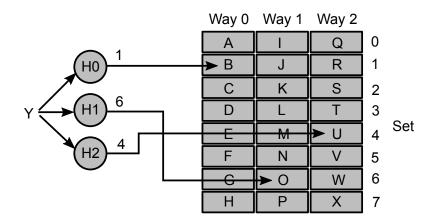

| 3.16                   | ZCache architecture.                                                                                            | 62 |

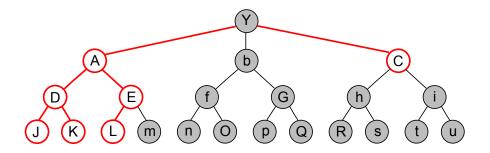

| 3.17                   | Tree of replacement candidates.                                                                                 | 63 |

| 3.18                   | Relocation to accommodate incoming cache block.                                                                 | 64 |

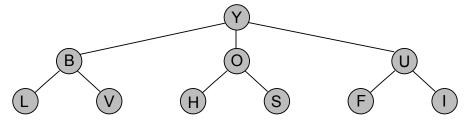

| 3.19                   | Same-domain replacement.                                                                                        | 65 |

| 3.20                   | A relocation-based attack.                                                                                      | 66 |

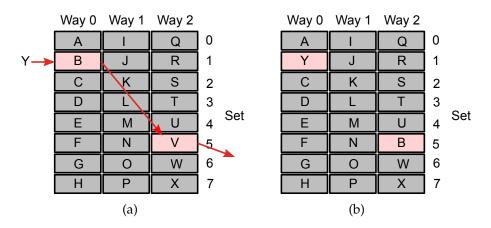

| 3.21                   | Strict same-domain replacement                                                                                  | 67 |

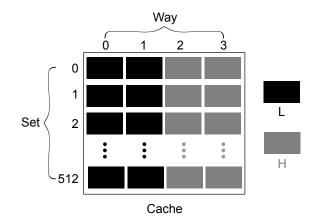

| 3.22                   | A partitioned cache.                                                                                            | 72 |

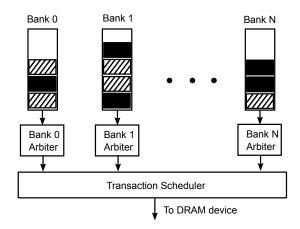

| 4.1                    | A conventional memory controller.                                                                               | 83 |

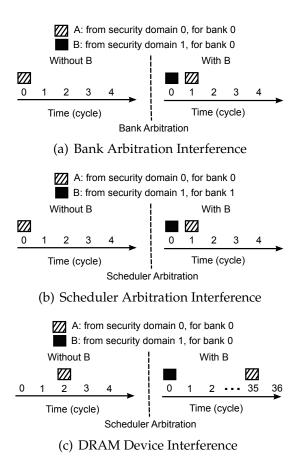

| 4.2                    | Interference in memory controllers.                                                                             | 84 |

| 4.3                    | System setup for an RSA attack.                                                                                 | 87 |

|                        |                                                                                                                 |    |

| 4.4  | Square and multiply algorithm for RSA: C is the encrypted mes-        |      |

|------|-----------------------------------------------------------------------|------|

|      | sage, x is the decrypted message, N is the product of two large       |      |

|      | prime numbers, d is the RSA private key, and n is the number of       |      |

|      | bits in the key.                                                      | 87   |

| 4.5  | RSA side-channel attack example.                                      | 88   |

| 4.6  | A covert-channel attack example.                                      | 89   |

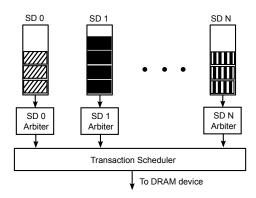

| 4.7  | Queueing structure per security domain.                               | 91   |

| 4.8  | Static time-slot allocation in temporal partitioning.                 | 91   |

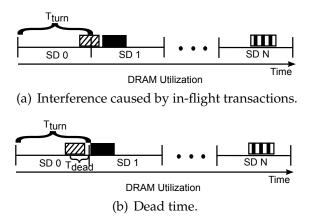

| 4.9  | Dead time to remove interference from in-flight transactions          | 94   |

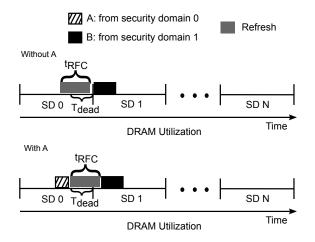

| 4.10 | Interference from a stalled refresh.                                  | 95   |

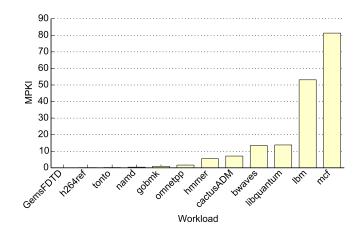

| 4.11 | Memory intensity study of SPEC2006 benchmarks                         | 100  |

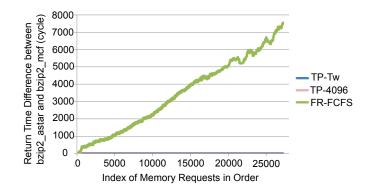

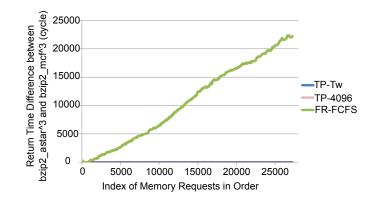

| 4.12 | Memory return time difference of $T0$ running with difference $T1s$ . | 101  |

| 4.13 | Memory return time difference with 4 security domains                 | 102  |

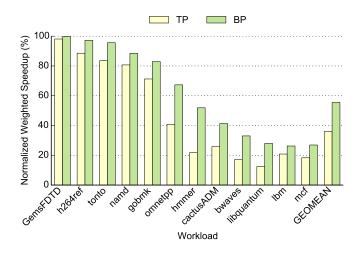

| 4.14 | Performance overhead of TP.                                           | 103  |

| 4.15 | Effect of turn length on performance overhead.                        | 104  |

| 4.16 | Performance improvement with bank partitioning.                       | 105  |

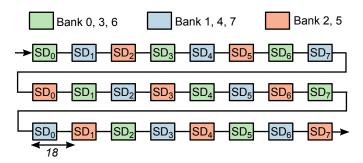

| 4.17 | Bank triple alternation schedule example                              | 107  |

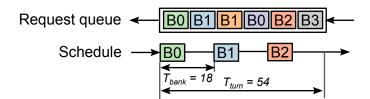

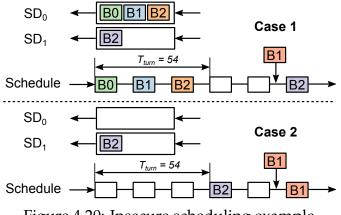

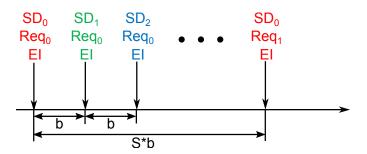

| 4.18 | SecMC-NI scheduling example.                                          | 109  |

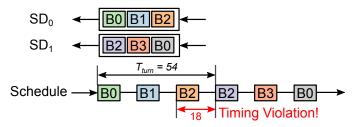

| 4.19 | Bank conflict in SecMC-NI scheduling.                                 | 109  |

| 4.20 | Insecure scheduling example                                           | 111  |

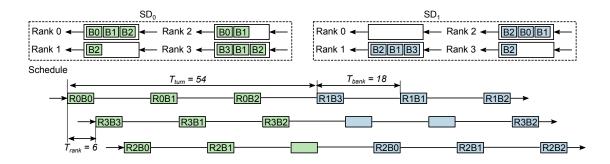

| 4.21 | SecMC-NI scheduling with rank interleaving.                           | 112  |

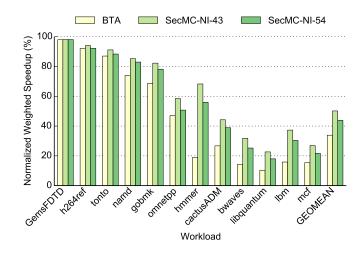

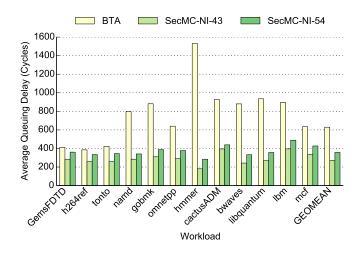

| 4.22 | Performance comparison between SecMC and BTA                          | 115  |

| 4.23 | Queuing delay comparison between SecMC and BTA.                       | 116  |

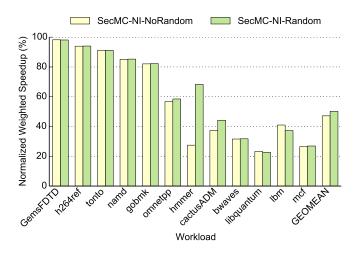

| 4.24 | SecMC with and without address randomization.                         | 117  |

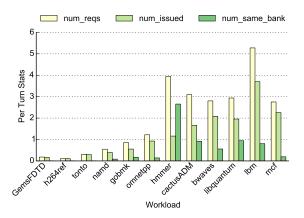

| 4.25 | SecMem scheduling statistics                                          | 117  |

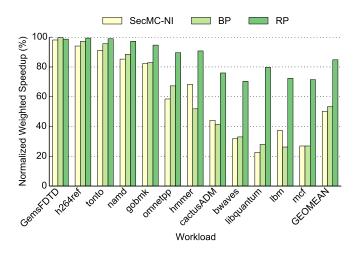

| 4.26 | Performance comparison between SecMC and spatial partitioning         | .118 |

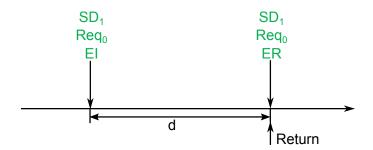

| 4.27 | Expected issue times for memory requests.                             |      |

| 4.28 | Expected response times for memory requests                           |      |

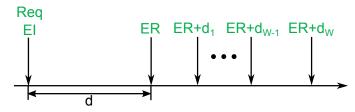

| 4.29 | Predetermined delay values.                                           | 124  |

| 4.30 | TP used as the worst-case scheduling algorithm                        | 125  |

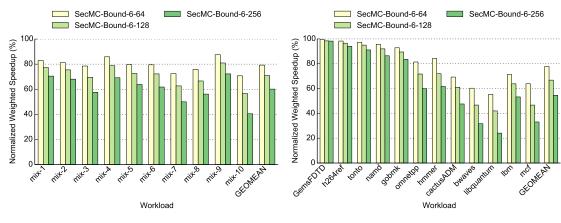

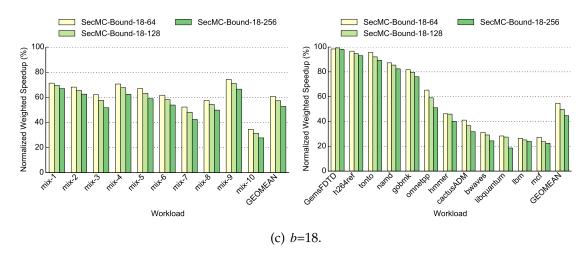

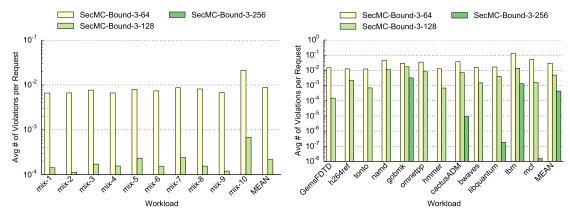

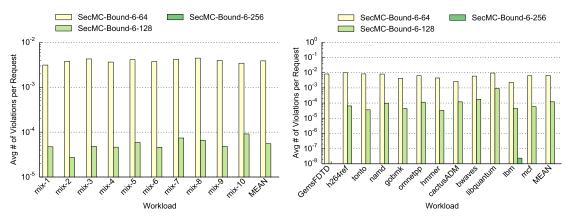

| 4.31 | Performance with different value of $b$ and $d$                       | 135  |

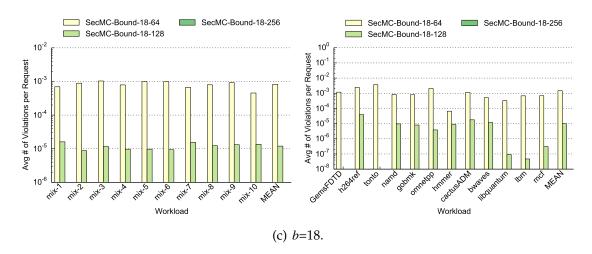

| 4.32 | Number of violations with different value of <i>b</i> and <i>d</i>    | 136  |

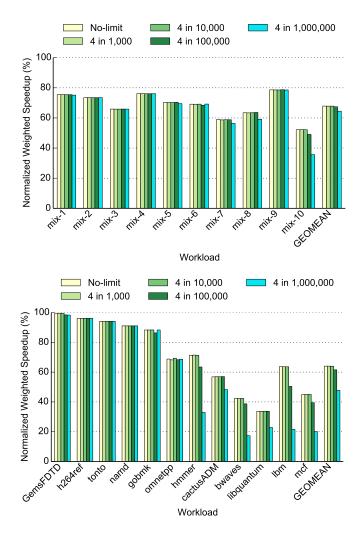

| 4.33 | Performance with limit on violations.                                 | 138  |

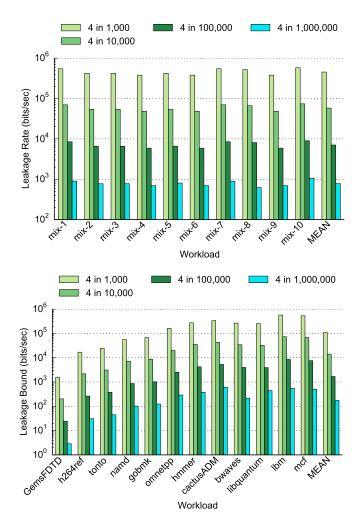

| 4.34 | Leakage rate with limit on violations.                                | 139  |

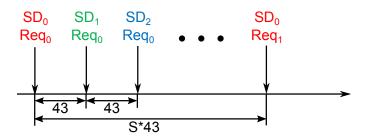

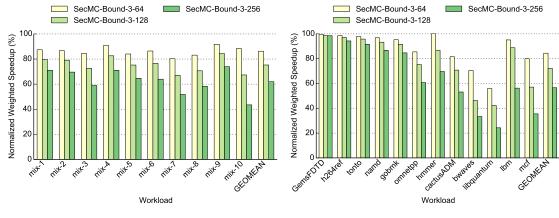

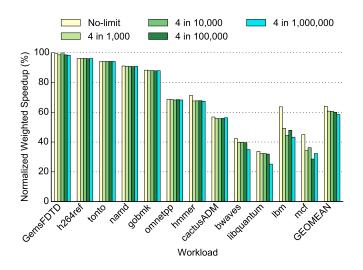

| 4.35 | Performance after optimization.                                       | 140  |

| 4.36 | Performance by tuning <i>d</i> 0 value                                | 141  |

| 4.37 | Combining SecMC-Bound with spatial partitioning                       | 142  |

| 4.38 | Performance comparison of different schemes.                          | 143  |

| 4.39 | Design space summary (mixed workloads).                               | 144  |

| 5.1  | A simple Verilog code example.                                        | 146  |

| 5.2  | Labeled code example                                                  | 147  |

| 5.3  | An insecure two-input mux.                                            | 148  |

| 5.4  | An example of implicit declassification                               | 149  |

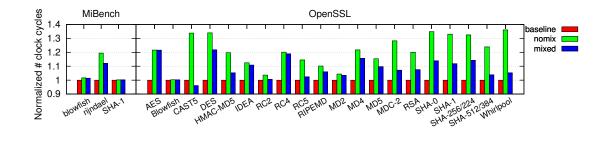

| 5.5 | Performance overhead of timing channel protection. | 156 |

|-----|----------------------------------------------------|-----|

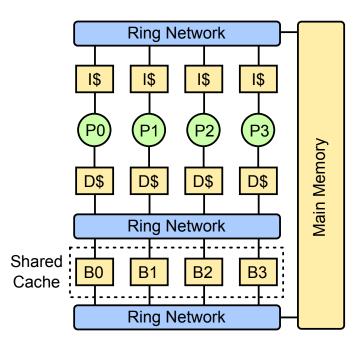

| 5.6 | Architecture of the multi-core processor.          | 157 |

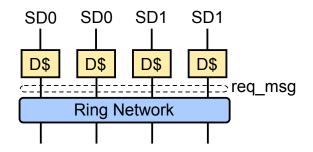

|     | A directory entry in bank 0.                       |     |

| 5.8 | Illustrative example for bit-level label support   | 162 |

## CHAPTER 1 INTRODUCTION

Multi-core processors are widely used in modern computing systems such as cloud servers and mobile devices. In the architecture of multi-core processors, some hardware resources are often shared by multiple cores to improve hardware efficiency. Each core can run a different application and contends for the shared resources such as caches, on-chip networks and memory. When competing for the shared hardware resources, applications can cause interference to each other, hence affecting individual program's execution time. This timing interference, unfortunately, can sometimes lead to timing channels, which are a type of an information channel that leaks confidential information through timing. Attacker applications can exploit timing channels to launch attacks to steal confidential information from victim applications. For example, previous work [RTSS09] has demonstrated a timing channel attack that reveals the keystrokes typed by a user through shared data caches on commercial Amazon EC2 servers.

Timing channel attacks introduce serious threats to modern computing systems. In cloud computing, a user's applications are scheduled to run concurrently with other applications, which could be malicious and try to infer confidential information that belongs to the user through timing channel attacks. A similar problem exists in mobile devices today. If a user downloads an application that contains malware, this malicious application might run concurrently with the user's banking application, stealing confidential information such as passwords. Timing channel attacks are hard to defend against because they do not rely on physical access to the system and can bypass today's security defense mechanisms such as access control. Even worse, a recent study [HKR<sup>+</sup>15] shows that timing channel attacks can also achieve a high leakage rate (500Kbps).

There exists extensive work on various hardware timing channel attacks and their countermeasures. However, most of the previous work focuses on cache timing channels. In this thesis, we explore possible timing channel attacks and their countermeasures in shared hardware resources including not only caches, but also on-chip networks and memory controllers. We find all these shared resources are vulnerable to timing channel attacks, and we develop efficient protection schemes that defeat these timing channel attacks. We further improve the performance of our protection schemes by introducing uni-directional protection when programs have asymmetric security requirements, or by trading off security for performance. Finally, we develop two processors in RTL and formally verify that both designs are free of timing channels using a tool called SecVerilog [ZWSM15].

## 1.1 A Case Study on Realistic Timing Channel Attacks

Previous work have proposed numerous timing channel attacks that exploit software or hardware vulnerabilities. Although many of these attacks were demonstrated in a confined environment, quite a few studies conducted their attacks in realistic environment settings including mobile devices and commercial VMs in cloud computing. These realistic timing channel attacks provide strong evidence that timing channel attacks are not only theoretically possible, but also practically viable as a way to leak confidential information. One notable work is a successful cache timing channel attack demonstrated on Amazon's EC2 cloud computing platform by Ristenpart et al. [RTSS09]. This section reviews Ristenpart's attack in more detail and also discusses other realistic timing channel attacks.

#### 1.1.1 Ristenpart's Attack on Amazon's EC2

As the cloud computing infrastructure continues to quickly evolve, more and more entities begin to export their computations and data into the cloud. While cloud computing brings several appealing benefits including economies of scale and dynamic provisioning, it also introduces new security threats as the computation and data of different entities (possibly rivals) could share the same physical machine. Traditional virtualization techniques (virtual machines) provides some degree of isolation between different entities, but does not offer complete non-interference because attacks (e.g., side-channel attacks) can bypass the boundaries between VMs. By far the best known example of a third-party compute cloud is Amazon's EC2, which is the target of the timing channel attack demonstrated by Ristenpart et al. [RTSS09]

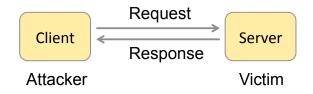

The proposed attack requires three steps to succeed. First, the attacker finds out the location of the victim VM in the cloud infrastructure to narrow down the search space. Second, the attacker tries to gain co-residence with the victim VM by spawning a set of VMs and checking for co-residence. Co-residence means the attacker VM and the victim VM reside on the same physical machine, which is the basis for many timing channel attacks. Lastly, the attacker VM extracts confidential information about the victim VM via a cross-VM attack, taking the form of timing channel attacks in this case. The three steps are described in more detail below.

#### Determining the Location of the Victim VM

When a user launches a VM, the VM is assigned to a single physical machine within the EC2 network for its lifetime. At the time of this attack being proposed, Amazon's machines were located in two regions, one in the United States and the other in Europe. Each region contains three availability zones. A user can specify a region and an availability zone to launch his or her VMs. Meanwhile, a user can also specify an "instance type" of the VM. Different instance types provide different computational power, memory and persistent storage. There were five Linux instance types, referred to as 'm1.small', 'c1.medium', 'm1.large', 'm1.xlarge', and 'c1.xlarge'.

In this step of the proposed timing channel attack, the attacker tries to determine the location (region and availability zone) of the victim VM in order to narrow down the search space of gaining co-residence. To achieve this goal, Ristenpart et al. did a survey study on instance mapping in Amazon EC2. They iteratively launched 20 VMs for each of the 15 availability zone/instance pairs and studied the relationship between the internal IP address of a VM and its zone or instance type.

Figure 1.1 shows the internal IP address mapping regarding different availability zones. The results suggest that the Amazon EC2 internal IP address is cleanly partitioned between availability zones. For example, samples from Zone 3 were assigned addresses within the range between 10.252.0.0/16 and

Figure 1.1: Internal IP address mapping regarding availability zones [RTSS09].

Figure 1.2: Internal IP address mapping regarding instance types [RTSS09].

10.253.0.0/16. While it is not surprising that availability zones show disjoint IP assignment, the experiments also shows a VM's instance type affects its IP address with considerable regularity. Figure 1.2 shows the internal IP address mapping regarding different instance types. This mapping study suggests that all /24 addresses between two consecutive Dom0 /24 addresses inherit the former's associated instance type. Here, Dom0 is a privileged virtual machine that is used to manage guest images, their physical resource provisioning, and any access control rights in Xen hypervisor [BDF+03]. For example, if one Dom0 VM is associated with m1.small with an IP address of 10.254.8.0/24 and the next Dom0 VM is associated with c1.medium with an IP address of 10.254.11.0/24, then any VMs that have IPs in prefixes 10.254.9.0/24 and 10.254.10.0/24 are associated with m1.small instance type.

The derived IP address mapping rules can dramatically reduce the number of instances needed before a co-resident placement is achieved. Basically, an attacker can enumerate public EC2-based web servers using external probes and translate responsive public IPs to internal IPs via DNS queries within EC2. With the internal IP address of a victim VM and the derived mapping rules described above, the attacker can figure out the availability zone and instance type of the victim VM. The attacker can then launch its VMs of the same instance type in the same availability zone to increase the chance of gaining co-residence.

#### Gaining Co-Residence with Victim VMs

Ristenpart et al. proposed several easy-to-implement network-based coresidence checks. Namely, instances are likely co-resident if they pass one of the checks listed below.

- Matching Dom0 IP address

- Small packet round-trip times

- Numerically close internal IP addresses (e.g., within 7)

As a matter of fact, an instance's network packet's first hop is always the Dom0 privileged VM. For the first check, an attacker can determine its own Dom0 IP from the first hop of any packet, and determine the Dom0 IP of another instance by performing a TCP SYN traceroute to the instance and inspecting the last hop. The second check is based on the fact that the packet round-trip times are usually smaller when two VMs are co-resident. The basis of the third check is that the same Dom0 IP will be shared by instances with a continuous sequence

of internal IP addresses. These checks were verified by comparing to the results of a hard-disk-based covert channel between EC2 instances and showed almost 100% accuracy.

Two strategies were proposed to gain co-residence with victim VMs. The brute-force strategy has an attacker launch many instances over time and targets on a set of victim VMs. In this strategy, the attacker repeatedly runs probe instances of the target type in the target zone, using the information gathered from the first step. Each probe instance performs the co-residence checks to determine if it is co-resident with any of the victim VMs. 1785 probe instances were launched in their experiments, which results in co-residency with 141 victim VMs out of 1686 target victims. Thus this strategy achieved 8.4% coverage of the target victim set. The second strategy exploits placement locality in Amazon EC2. Basically, if two instances run sequentially (the first terminated before launching the second) or run at around the same time, they are likely to be assigned to the same machine. In this attack strategy, the attacker detects when a victim VM is launched, and then engages in *instance flooding*: running as many instances in parallel as possible in the same availability zone and of the same instance type. Because of the placement locality exhibited by the EC2 placement algorithm, the attacker is able to achieve co-residence with a target victim VM 40% of the time (launching just 20 probe instances)—a very high successful rate. The assumption that the attacker can detect when a victim VM is launched is based on that an attacker can monitor a server's state by constant network probing. More interestingly, an attacker might be able to trigger new victim instances due to the use of auto scaling systems. The success of gaining co-residence with victim VMs was even demonstrated on commercial instances from companies including RightScale and rPath.

#### **Carrying Out Timing Channel Attacks**

Once an attacker places its VM on the same physical machine as a victim VM, he or she can extract confidential information (e.g., cryptographic keys) from the victim VM through various timing channel attacks. Ristenpart et al. demonstrated a cache-based timing channel attack that allows an attacker to measure the cache usage of a victim VM that shares the same cache with the attacker VM. The attack can also be used to estimate the traffic rates of a co-resident web server, which may correlate with confidential information. Both attacks were demonstrated in the Amazon EC2 environment, which represents the realistic environment settings in cloud computing. Although the demonstrated attacks were relatively simple, the main contribution of this work is that it shows a practical attack step by step in the real world. Since attackers can easily gain co-residence with victim VMs, various timing channel attacks that are based on hardware resource sharing (including the ones that will be described in this thesis) become viable to the attackers.

## **1.1.2** Other Realistic Timing Channel Attacks

As an extension to Ristenpart's attacks [RTSS09], Zhang et al. [ZJRR12] proposed a more fine-grained cache-based timing channel attack between VMs that share the same physical machine. In this attack, the attacker is able to probe the cache very frequently by abusing interprocess interrupts (IPIs), and filter out the noise due to hardware and software features. The fine-grained cache probing allows the attacker to extract a private ElGamal decryption key [EG85] from a co-resident victim VM. The attack was demonstrated on an Intel Core 2 Q9650 processor. It shows that probing over the course of just a few hours can provide the attacker enough information to reconstruct the victim's 457-bit private key with high accuracy—fewer than 10,000 possible keys need to be searched to find the right one!

Another line of work on timing channel attacks exploits timing difference in write accesses on deduplicated memory pages. Memory deduplication is a technique to reduce the memory footprint of a system by combining identical pages. However, write access to these deduplicated pages leads to a page fault, which takes much longer to process than write access to normal pages. This timing difference serves as the basis for several timing channel attacks. Suzaki et al. [SIYA11] proposed an attack that can determine whether specific applications are running in a co-located virtual machine in the cloud. Owen et al. [OW11] demonstrated that it is possible to efficiently fingerprint operating systems of co-resident virtual machines using memory deduplication attacks. Attackers can use OS fingerprinting to learn the type and version of an operating system so that they can launch attacks that are specific to the target OS. Gruss et al. [GBM15] presented a page deduplication attack in sandboxed JavaScript, which allows a remote attacker to collect private information such as whether a program or website is currently opened by a user. The proposed countermeasure was to disable page deduplication completely.

Many of the timing channel attacks take the form of passive attacks, which means the attacker can gain information about the victim system without noticeably affecting the behavior of the target system [ZF05]. Passive attacks are quite difficult to detect, and they can result in hazards to security and privacy. Because of these potential attacks, many companies refuse to outsource their computational tasks to public computing infrastructures. According to a recent IDCI survey, 74% of IT executives and CIOs cited security as the top challenge preventing their adoption of cloud services [SK11b]. It is thus important to build a secure computing environment that can defeat various kinds of attacks, including timing channel attacks. However, current countermeasures against timing channel attacks suffer from either inflexibility or high performance overhead, which make them hard to deploy in practice. As a result, timing channel attacks remain to be a continuing threat in computing systems in the near future. This thesis explores some flexible and efficient timing channel protection schemes as a first step towards building systems that are invulnerable to timing channel attacks.

### 1.2 Threat Model

To defend against timing channel attacks, we first describe our threat model, which defines security objectives and identifies vulnerabilities and threats. On a high level, our threat model assumes a multi-core processor as the target platform and a hierarchical security policy.

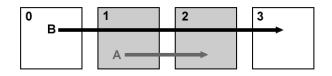

## **1.2.1** Baseline Architecture

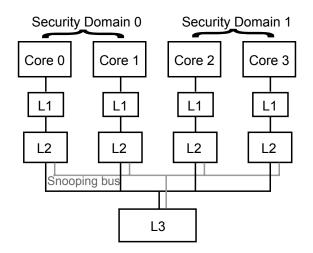

The timing channel attacks and protection schemes in this thesis target a multicore processor, as shown in Figure 1.3. The processor has multiple in-order or out-of-order cores. All cores share a large last-level cache (LLC), which is connected to the private caches through on-chip networks. The networks can

Figure 1.3: Baseline architecture.

be any topology that is applicable, such as bus, ring or mesh networks. The LLC is connected to a memory controller, which handles memory requests and responses.

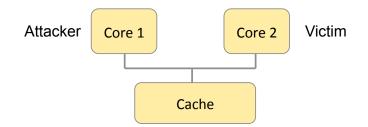

In this multi-core architecture, three major hardware components (on-chip networks, LLC, memory controller) are shared among all the cores. Since each core can run a different application, a malicious application can steal information from another application through timing channel in these shared components. This thesis focuses on discovering possible timing channel attacks and developing their countermeasures in these shared components.

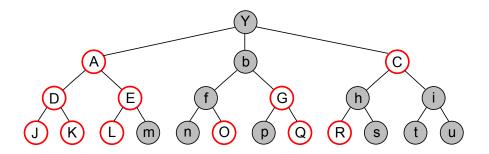

## **1.2.2 Hierarchical Security Policy**

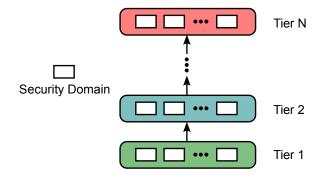

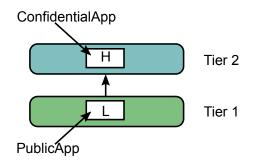

Our threat model considers timing channel protection among security domains. A security domain is defined as a set of software modules (VMs, processes, threads) that do not need timing isolation among them. As an example, consider the cloud computing platform in Figure 1.4. A security domain may contain multiple VMs if these VMs belong to the same user. The hypervisor/OS is

Figure 1.4: Security domains in cloud computing.

Figure 1.5: Hierarchical security policy.

responsible for scheduling these VMs to the underlying processor and tagging each VM with the correct security domain ID.

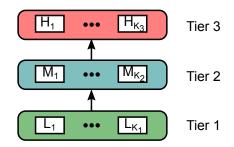

Different security domains may pose different security requirements. This thesis assumes a hierarchical security policy that defines the relationship between security domains, as shown in Figure 1.5. There are *N* security tiers, and each tier contains an arbitrary number of security domains. The security policy follows the rule below:

Figure 1.6: Common security policies.

Information is allowed to flow from security domain *A* to security domain

*B* if and only if *A* ∈ Tier *i*, *B* ∈ Tier *j* and *i* < *j*.

The security policy has two implications. First, information may not flow between two security domains in the same security tier. This is useful for the use case where multiple mutually distrusting high security applications (e.g., banking, medical) are running concurrently. Second, information **is** allowed to flow from a lower security tier to a higher security tier. This represents the use case where low security applications (e.g., simple games) are running together with high security applications. Information is allowed to flow from low security applications to high security applications, but not the other way around.

The security policy is general enough to support common use cases. For example, a government or military database system usually employs the multilevel security (MLS) policy, which consists of four hierarchical levels. This MLS policy can be represented in our security policy by four security tiers with each tier containing one security domain, as shown in Figure 1.6(a). The security policy can also represent the mobile scenario with two security tiers, as shown in Figure 1.6(b). Tier 1 only has one security domain *L*, which contains public applications. Tier 2 has two security domains, with each security domain containing a different high security application.

## 1.2.3 Attack Assumptions

Timing channel attacks can take many different forms. In general, timing channel attacks can be divided into software-based attacks and hardware-based attacks. Software-based attacks exploit the vulnerabilities in software, while hardware-based attacks rely on the microarchitectural features of a processor. This thesis focuses on defending against hardware-based timing channel attacks. More specifically, we consider attacks that exploit interference in shared hardware resources between **concurrently running** programs. Hardware timing channels within a program or caused by context switches are out of the scope of this thesis. As an exception, a couple of secure cache designs are proposed to defeat cache timing channels within a program in Section 3.6.

Both unintentional and intentional information leaks are considered in this threat model. Thus, I aim to prevent both side-channel and covert-channel attacks. The goal of a side-channel attack is to gain access to the secret information possessed by the victim, which does not intend to leak the secret. The attacker can intentionally create interference in the shared hardware resources and make timing measurements on its own operations. The attacker then tries to correlate the timing information with the secret. In a covert-channel attack, the attacker already possesses a secret, but is limited in how it can share this secret. For example, a malicious 3rd party web application may try to leak a user's data when the cloud infrastructure restricts its network connections so that it cannot directly communicate with malicious servers. The attacker can try to bypass such restrictions using a timing channel to communicate with a co-resident VM whose network connection is not restricted. The attacker can communicate the secret by deliberately modifying its workload to cause timing variations to the colluding attack program's execution.

The threat model assumes a strong attacker. The attacker can generate any pattern of cache accesses as well as memory requests, which gives the attacker the capability to create interference that favors timing channel attacks in the shared resources. Another assumption is that the attacker is able to measure the exact timing of its own memory accesses so that it can analyze the timing information with high accuracy. On the other hand, the hypervisor/OS is assumed to be trusted and not compromised by the attacker. The hardware counters are controlled by the hypervisor/OS and are not accessible by the attackers. For most of this thesis except for Section 3.6, we assume different security domains do not share data that can be both read and written. However, different security domains are allowed to share read-only data (e.g., program code, shared library.).

## **1.3 Limitations of Software-Only Solutions**

One approach to protect against timing channel attacks is to write or rewrite software in a way that defeats known timing channel vulnerabilities. However, this approach has several limitations. First, software solutions are often designed to deal with only specific timing channel attacks. The software written with a timing channel protection method is still vulnerable to new timing channels that have not yet been revealed. For example, the Montgomery multiplication [Mon85] and Chinese Remainder Theorem implementation of Diffie-Hellman [DH06] or RSA [RSA78] were believed to defeat the timing attack designed by Kocher [Koc96a]. However, this implementation is shown to be prone to a later attack proposed by Brumley et al. [BB03]. The second limitation of software solutions is the lack of precise control on execution time. To illustrate the idea, consider a simple code snippet below.

> 1 Victim: 2 int secret, h1, h2, l1; 3 init(secret, h1, h2, l1); 4 5 if (secret) 6 h1 = l1 7 8 h2 = h1

If the value of *secret* is 1, line 6 is executed. Otherwise, line 6 is skipped. The timing difference reveals the value of *secret*—a timing channel. One naive solution to eliminate the timing channel is adding dummy operations to balance the control flow, as shown below.

```

1

Victim:

2

int secret, h1, h2, l1, l2;

3

init(secret, h1, h2, l1, l2);

4

5

if (secret)

6

h1 = 11

7

else

8

12 = 11

9

10

h2 = h1

```

At first glance, this software fix seems to work because both branches of the *if* statement have the same number of instructions. However, it ignores the underlying hardware features such as caches. If the value of *secret* is 1, *h*1 is brought into a cache, hence the execution time of line 10 is short because of a cache hit. If the value of *secret* is 0, the access to *h*1 in line 10 becomes a cache miss. The timing difference between a cache hit and a cache miss represents a timing channel that can reveal the value of *secret*.

The timing channel shown in the example above is caused by the cache interference between different instructions within the same program. Timing channels may also be introduced by interferences between different processes in shared hardware resources. For example, a victim program's cache accesses may evict cache lines of an attacker in a shared LLC, which allows the attacker to infer confidential information about the victim. It is also possible that a victim's memory requests delay the memory requests of an attacker when competing for the same memory channel, resulting in illegal information leakage. Many software solutions are prone to similar timing channels because software cannot strictly control the execution time of each instruction.

Software-only solutions are insufficient to defend against these microarchitectural timing channel attacks due to the limitations discussed above. Protection mechanisms must also be implemented in hardware to completely eliminate the sources of timing channels. To this purpose, my thesis will focus on designing efficient timing channel protection mechanisms in hardware.

## 1.4 Thesis Contribution and Organization

This thesis proposes timing channel protection mechanisms for shared hardware resources in a multi-core processor. The goal of these protections is to defend against timing channel attacks between concurrently running programs while minimizing the performance overhead introduced by the protection. Depending on the specific security policy, timing channel protections in this thesis are divided into three approaches.

If two security domains are mutually distrusting (i.e., they are in the same security tier), the protection scheme needs to ensure that information does not flow in either direction. This kind of protection is called **bi-directional protection**. Bi-directional protection requires complete noninterference between security domains, which poses restrictions on how the shared resources can be used by different security domains and can significantly degrade performance.

On the other hand, if two security domains are not in the same security tier (e.g., L and  $H_1$  in Figure 1.6(b)), the protection scheme only needs to guarantee

the information does not flow from the higher security tier to the lower one. This kind of protection is called **uni-directional protection**. Uni-directional protection allows the runtime information from the security domain in a lower security tier to be used to decide how the hardware resources are allocated to higher tiers. With the help of this runtime information, uni-directional protection can generally provide more efficient resource allocations or scheduling decisions compared to bi-directional protection, as will be shown in later chapters.

Both bi-directional and uni-directional protections prevent any illegal information flows according to the security policy, i.e., they enforce zero information leakage. However, users sometimes are willing to sacrifice security for better performance. A third approach to defend against timing channel attacks allows controllable amount of information leakage between security domains while trying to maximizing the system performance. This approach enables a tradeoff between security and performance, which allows the users to tune the performance of their systems based on the amount of information leakage they can tolerate.

In the rest of this thesis, all three design approaches are used to develop efficient timing channel protection schemes for the shared hardware resources in a multi-core processor. The primary contributions of this thesis are summarized below:

• We construct a timing channel attack against on-chip networks. We propose a bi-directional protection scheme called Temporal Network Partitioning (TNP), as well as a uni-directional protection scheme called Reverse Priority with Static Limit (RPSL). Both schemes eliminate the timing channels in on-chip networks.

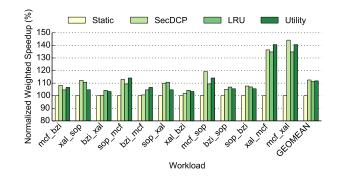

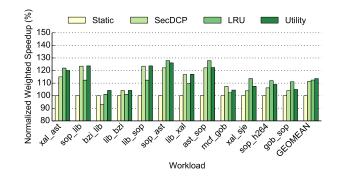

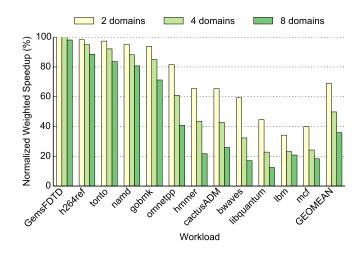

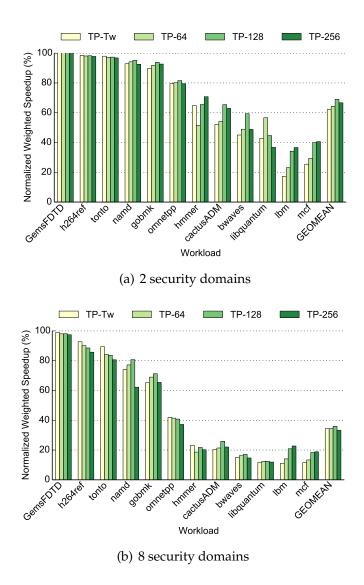

- We identify timing channel attacks against caches and propose several protection schemes. We found that timing channel attacks are possible through cache coherence protocols and defeat the attacks with simple time-division multiplexing mechanisms. We develop a secure dynamic cache partitioning scheme (SecDCP) that defeats cache timing channel attacks with uni-directional protection. SecDCP improves performance by up to 43% and by an average of 12.5% over static cache partitioning. Furthermore, we propose a secure cache design based on a high-associativity cache (ZCache [SK10]) to support more security domains. We also find a possible attack caused by the relocation process of ZCache. To defend against timing channels within a program, we propose a couple of secure cache designs (DirtyCache, RelCache) that supports software security labels.

- We construct timing channel attacks against shared memory controllers. We propose two completely secure memory controller designs (TP and SecMC-NI). SecMC-NI improves the performance of the best known scheme by 45%. To further improve the performance, we also propose a memory controller that enables a tradeoff between performance and security (SecMC-Bound).

- We implement some of the protection mechanisms in RTL. Two secure processors are developed and verified using a tool called SecVerilog [ZWSM15]. The results show that the protection mechanisms indeed remove timing channels at the gate level.

Table 1.1 summarizes the contributions of this thesis. The rest of the thesis is organized as follows. Chapter 2 describes our findings on new timing

| Hardware              | Bi-directional<br>Protection | Uni-directional<br>Protection    | Performance<br>and Security<br>Tradeoff |

|-----------------------|------------------------------|----------------------------------|-----------------------------------------|

| On-Chip<br>Networks   | TNP                          | RPSL                             |                                         |

| Caches                | ZCache-Based<br>Protection   | SecDCP<br>DirtyCache<br>RelCache |                                         |

| Memory<br>Controllers | TP<br>SecMC-NI               |                                  | SecMC-Bound                             |

Table 1.1: Primary contributions of this thesis.

channel attacks against on-chip networks and our protection schemes using bidirectional and uni-directional protection. Chapter 3 discusses previous timing channel attacks on caches and introduces our secure cache designs. Chapter 4 presents our studies on new memory controller timing channel attacks and protection mechanisms. Chapter 5 discusses our experience of designing two secure processors in RTL and verifying their timing channel security using SecVerilog. Finally, Chapter 6 summarizes related work and Chapter 7 concludes the thesis and discusses future directions.

# **1.5** Collaboration, Previous Publications, and Funding

This work would not have been possible without the effort of all my collaborators. My advisor, Professor Edward Suh, was the key collaborator in brainstorming all the timing channel protection ideas. Andrew Ferraiuolo helped develop the simulation infrastructure needed to evaluate the memory controller protection schemes. His expertise in timing channel protection also helped me quickly identify security vulnerabilities in the early design of protection schemes for caches and memory controllers. The hierarchical security policy was also inspired by Andrew's work on Lattice Priority Scheduling [FWZ<sup>+</sup>16]. Danfeng Zhang is the creator of SecVerilog, which is the tool that allows me to verify the security of a hardware design down to the gate level. His work on language-based protection framework inspires my work on the secure cache design that supports software security labels. Danfeng also helped evolving the secure cache design as well as the secure dynamic cache partitioning scheme, SecDCP. Professor Andrew Myers was a great resource for insights into developing efficient timing channel protections and applying SecVerilog in hardware designs. Andrew also offers a lot of educational suggestions in terms of paper writing. I would also like to acknowledge Rui Xu for his work in developing secure processors using SecVerilog. His experience in SecVerilog helped me quickly solve difficulties I encountered when verifying secure processors with SecVerilog. I also want to thank Professor Christopher Batten and his group (Ji Kim, Shreesha Srinath, Chris Torng, and Berkin Ilbeky) for providing me with the source code of the PARC-tiny processor for RTL verification.

This thesis includes my work of several previous publications, including timing channel attacks and protections for on-chip networks [WS12], caches [WFZ<sup>+</sup>16] and memory controllers [WFS14, WWS17]. I helped Danfeng Zhang to test and validate the design of SecVerilog [ZWSM15] by applying SecVerilog to the design of a secure MIPS processor. The results of the MIPS processor design are included in this thesis. I also helped Andrew Ferraiuolo to develop a uni-directional protection scheme for memory controllers called Lattice Priority Scheduling [FWZ<sup>+</sup>16], which is not included in this thesis.

In terms of funding, the work in this thesis was supported in part by NSF CNS-0746913, NSF CNS-0708788, NSF CNS-0905208, NSF CNS-0746913,

NSF CCF-0905208, NSF CNS-1513797, AF FA8750-11-2-0025, ONR N00014-11-1-0110, ARO W911NF-11-1-0082, and donations from Intel Corporation.

# CHAPTER 2

### **ON-CHIP NETWORKS**

This chapter discusses timing channel attacks and protection schemes for shared on-chip networks. Section 2.1 describes timing channel attacks we found in shared on-chip networks. Section 2.2 describes a bi-directional protection scheme based on Temporal Network Partitioning (TNP). We then propose a more efficient uni-directional protection scheme called Reverse Priority with Static Limits (RPSL) in Section 2.3.

### 2.1 Attacks

# 2.1.1 On-chip Network Interference

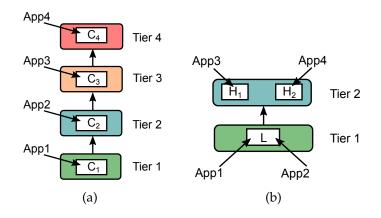

On-chip network interference happens when network flows from multiple applications contend for shared resources such as links and buffers. As an example, Figure 2.1(a) illustrates a simple scenario where two flows, Flow *A* and Flow *B*, share a common link between Node 1 and 2 on a typical 1-D mesh with 4 virtual channels. Because only one flow can use the link in each cycle, the network performance of one flow, such as throughput and latency, can be affected by the other flow's demand. Figure 2.1(b) and Figure 2.1(c) show the throughput of Flow *A* and *B* respectively as a function of the other flow's injection rate, using a cycle-level network simulator called Darsim [LSC+10]. In the experiments, we fixed one flow's injection rate (0.2, 0.5, or 1 flit/cycle) and measured its delivered throughput while varying the other flow's injection rate from 0 to 1 flit/cycle. As shown in the figure, when a flow has a low injection rate (0.2 flit/-

(a) Network and flow setup.

Figure 2.1: A simple network interference example.

cycle), its throughput is not significantly affected by the other flow's injection rate because a round-robin arbitration allocates roughly half of the link capacity to each flow, which is enough to satisfy the demand. However, when the injection rate is high (1 flit/cycle), a flow's throughput is highly dependent on the other flow's injection rate.

This network interference can be exploited as a vector to launch timing channel attacks. Essentially, an attacker can measure its run-time network throughput or latency to infer what the victim is doing (e.g., the victim's run-time network demand) and further correlate this information with the victim's secret.

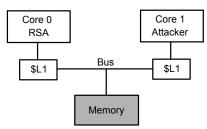

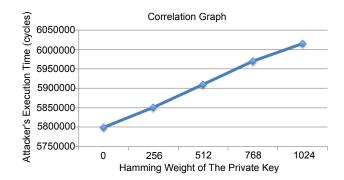

# 2.1.2 An RSA Attack

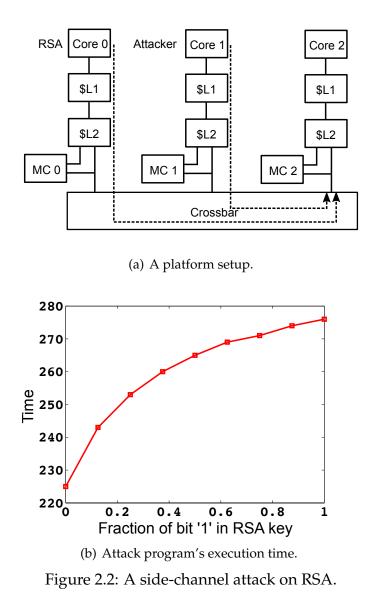

As a more concret example, let us consider a timing channel attack on the RSA [RSA78] algorithm, as shown in Figure 2.2. RSA is a public key cryptographic algorithm that is widely used to secure electronic communications through encryption or digital signatures. In one of the RSA implementations, the core algorithm performs a modulo multiplication of two large numbers (often 1024 or 2048 bits) depending on each bit in a secret key, and is shown to be prone to tim-

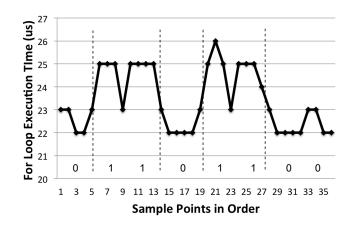

ing attacks [Koc96b]. Essentially, the algorithm examines each bit in the key and only performs a multiplication if the bit is 1. In this example, the multiplication operation in RSA causes additional network traffic to the memory controller 2 (MC2) due to cache conflicts. Meanwhile, the attack program runs a loop that generates cache misses in every iteration, which also sends a lot of memory requests to MC2. Packets from the RSA program and the attack program share the output port of the crossbar and experience network interference. The experiments were performed using McSim [ALOJ13], which provides timing models for a multi-core platform based on Intel's Pin [LCM+05] tool. Figure 2.2(b) shows the attack program's execution time as the number of 1s in the RSA key varies. As shown in the figure, the execution time has a direct correlation with the fraction of 1s in the key. This result suggests that the attacker can roughly estimate the number of 1s in the key based on its own execution time, which can greatly reduce the search space to find the correct key.

# 2.2 Temporal Network Partitioning (TNP)

We propose to use temporal network partitioning to defend against timing channel attacks for on-chip networks. In this protection scheme, we statically allocate virtual channels (VCs) in each input port of a router to security domains. We then use oblivious arbitration [DT04] to have security domains take pre-determined turns to use the crossbars and links on a per-cycle basis. In the case of two security domains, each security domain can be allocated with a half of input virtual channels for exclusive use, and be allowed in the switch allocation and link traversal in every other cycle. Effectively, this scheme statically allocates a half of network resources to each domain. Since the allocation is completely static, the attacker is unable to infer any dynamic demand about the victim using on-chip network interference.

TNP removes a timing channel in both directions between two security domains. However, it can incur significant performance overheads because resource allocation cannot be dynamically adjusted to match the actual network demands from each security domain. For example, if one security domain has a high bandwidth demand while the other domain has a very low demand, TNP only allows the domain with the high demand to use at most half of the network bandwidth. To solve this problem, TNP can be configured to statically allocate more bandwidth to the security domain with higher demand. However, since the bandwidth allocation is always static, TNP cannot efficiently deal with bursts or changes in different phases of an application.

Another bi-directional protection scheme called "SurfNoC" [WGO<sup>+</sup>13] has been proposed recently to improve the performance of TNP. SurfNoC also builds on top of time division multiplexing the network resources among different security domains, but came up with a better scheduling of security domains in each router, which allows a packet to be forwarded to the next router immediately after it arrives. This smart scheduling avoids the unnecessary delay for a packet to stay in the input buffers and wait for its turn.

# 2.3 **Reverse Priority with Static Limit (RPSL)**

TNP completely eliminates timing channels in on-chip networks, but can be quite inefficient because all network resources are statically allocated. In this section, we propose a more efficient protection scheme that allows dynamic scheduling of network traffic through uni-directional protection.

# 2.3.1 Priority-Based Arbitration

In the multi-level security model, one goal is to prevent information flows from the high security domain to the low security domain. To achieve this goal without statically allocating resources, we propose a priority-based arbitration for resources such as the router crossbar. The basic idea is to assign a high priority to low security traffic so that its behavior is not affected by high security traffic. In other words, when flows from two security domains compete for the switch traversal, the low security domain always wins, in both input port and output port arbitrations in a separable allocator. To remove interference in buffers, virtual channels are statically allocated to each security domain. This static allocation removes head-of-line blocking between packets from different security domains. In this way, the low security flows are not affected by the dynamic demands of the high security flows. At the same time, this approach allows a security domain to dynamically use more network resources when the other domains have low demands.

# 2.3.2 Denial-of-Service Protection

While assigning a higher priority to a lower security domain can prevent illegal information leakage without statically restricting network resources, the approach introduces an obvious concern for fairness. In fact, the strictly higher priority allows a malicious program in the low security domain to easily perform a Denial-of-Service (DoS) attack on high security programs by sending packets at a high injection rate and occupying all network resources.

To prevent the DoS attack, we add an additional mechanism that monitors and limits the traffic amount of the low security domain in a way that is independent from the demand of the high security domain. This mechanism sets a static limit per port on the number of flits that can be sent by the low security domain over a certain time interval. Once the limit is reached, the port does not send the low security flits until the next interval, allowing the high security flits to go through. For example, if we set the limit to be 80 and time interval to be 100, it means the low security flows can at most send 80 flits every 100 cycles. The remaining cycles can only be used by the high security flows. Note that the static limit does not create a timing channel because it does not depend on the high security traffic. Also, the limit can change over time for better performance as long as it does not reflect sensitive information from the high security domain.

# 2.3.3 Multiple Security Domains

It is relatively straightforward to extend the protection scheme to support more than two security domains. Suppose we have *N* security domains, and we rank them based on their security tiers. The flows from the lowest security domain get the highest priority to use the router crossbar and vice versa. To extend to *N* security domains, RPSL needs *N*-1 static limits to avoid DoS attacks, one for each domain except for the highest security domain. The limits may specify the maximum bandwidth usage over a certain period for corresponding security domains or the aggregate maximum usage for each security domain and below.

# 2.3.4 Evaluation

#### **Experimental Setup**

We evaluate the proposed protection scheme, named RPSL, compared to the baseline without protection and TNP. The simulations are performed by modifying Darsim [LSC<sup>+</sup>10]. The network is configured with four virtual channels per port, and uses iSLIP [DT04] as the baseline allocator. We assume a low security domain and a high security domain. For TNP, we allocate half of the virtual channels and switch time slots to each security domain. For RPSL, we allocate half of the virtual channels to each domain while prioritizing the low security flows in arbitration. The static limit in RPSL is set to be 80 flits per 100 cycles. Each packet consists of eight data flits and one head flit. All the experiments are done with a warm-up period of 20,000 cycles, followed by simulation of 100,000 cycles.

#### **Security Evaluation**

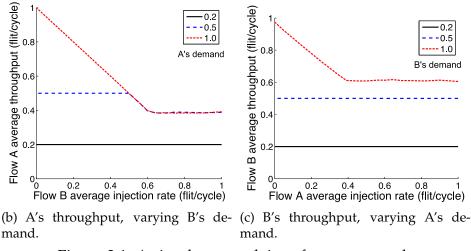

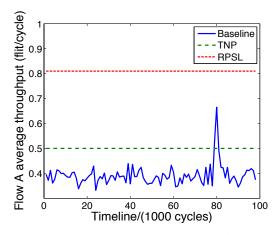

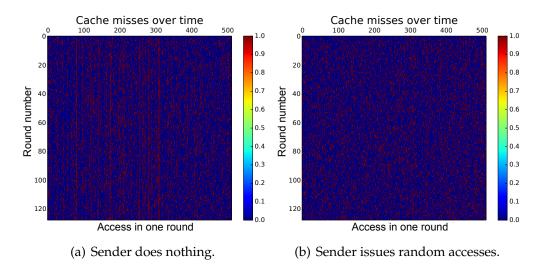

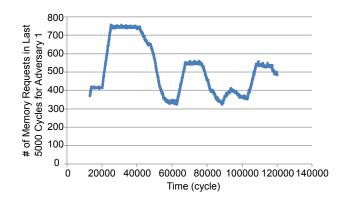

We study the security of each protection scheme using the simple example shown in Figure 2.1. In the experiments, we assign Flow *A* to be the low security flow and Flow *B* to be the high security one. In practice, an attack program will measure its throughput over time while keeping its injection rate high. The variations in the observed throughput is used to obtain information about the

Figure 2.3: Flow A's throughput over time with varying demands from Flow B. Flow A: low security, Flow B: high security.

victim. To mimic such an attack process, we keep Flow *A*'s injection rate at 1 flit/cycle while varying the injection rate of Flow *B* over time. More specifically, we randomly change the injection rate of Flow *B* among 1/3, 1/2, and 1 flit/cycle every 1000 cycles.

Figure 2.3 shows the dynamic throughput of Flow *A*. In the baseline scheme, the throughput of Flow *A* varies significantly over time, which reflects the dynamic demands of Flow *B*. This shows the baseline scheme is vulnerable to timing channel attacks. On the other hand, the throughput of Flow *A* stays constant under TNP and RPSL, regardless of the changing injection rate of Flow *B*, which shows the information leakage from the high security domain to the low security domain is prevented.

### **Performance Evaluation**

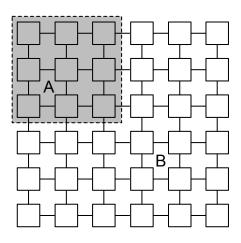

We evaluate the performance of the protection schemes on a 6-by-6 mesh network with two security domains. As shown in Figure 2.4, domain *A*, which is

Figure 2.4: Experimental setup in a 6-by-6 mesh network.

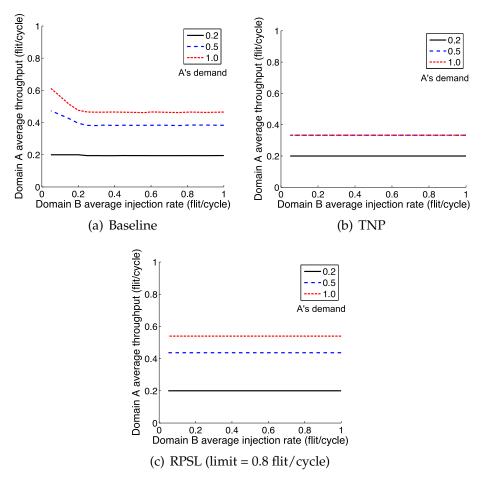

the low security domain, was given one-fourth of the cores. We place the cores in contiguous locations because this minimizes the communication cost within a security domain. We simulated a transpose traffic pattern in which a node communicates with the node that is symmetric with respect to the diagonal. We use Y-X routing in this experiment. As a result, flows from different domains share some links in the network, potentially causing interference. We tested three injection rates (0.2, 0.5, 1.0 flit/cycle) for the low security domain. We plot the average throughput of the low security domain while varying the average injection rate of the high security domain, which shows if there exists a timing channel from the high security domain to the low security domain.

Figure 2.5 shows the performance results. As expected, in the baseline scheme, the throughput of domain *A* (low security) changes with the injection rate of domain *B* (high security). In contrast, domain A's throughput stays constant under both TNP and RPSL. Again, this shows both schemes provides an effective protection against timing channels. On the performance side, a distinct difference between the results of TNP and RPSL is that domain *A* achieves higher average throughput in RPSL than in TNP when domain *A*'s injection rate

Figure 2.5: Low security (domain A) throughput as a function of the high security (domain B) demand for transpose traffic pattern.

is high (0.5 or 1 flit/cycle), which shows the performance advantage of RPSL over TNP scheme by allowing more efficient sharing of network resources. We also tested hotspot traffic pattern and the results show similar trends.

The experiments above keep the injection rate constant in each simulation run. To mimic the real application behavior, we simulated the transpose traffic pattern again but randomly vary the injection rate of each flow at run time. We measure the throughput of each domain as well as the aggregate throughput of the system, as shown in Figure 2.6. We normalize the actual throughput over throughput demand, which equals to the number of flits received divided by

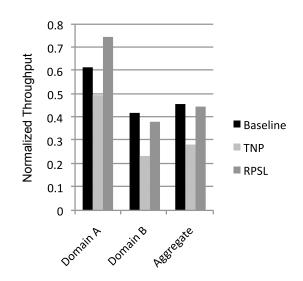

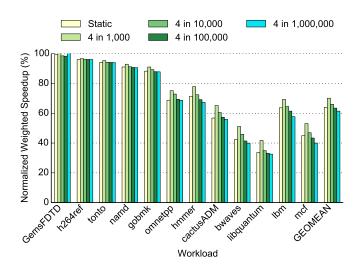

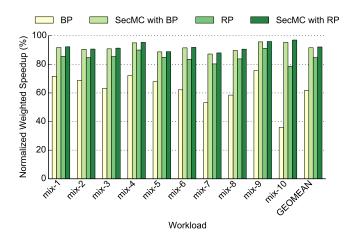

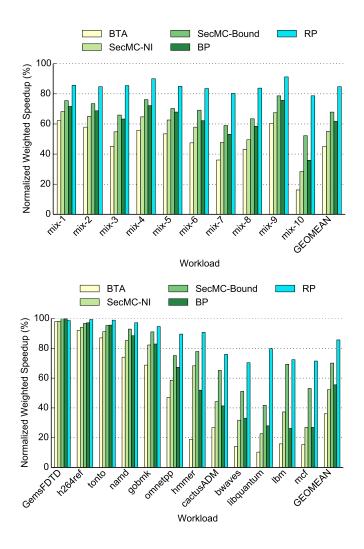

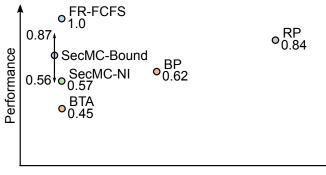

Figure 2.6: Impacts of timing channel protection on the network throughput.